FRAMOS‘s SLVS-EC RX IP Core Development Kit comes with comprehensive support for those looking to connect with sensors using the SLVS-EC interface. This new, scalable, 2.0 version SLVS-EC high-speed interface supports a higher data rate for all 8 lanes at 5 Gbps throughput per lane, up from the previous 2.5Gbps speeds. Engineers developing solutions using Xilinx FPGAs and SoCs can now take advantage of FRAMOS’s SLVS-EC RX IP Core, Evaluation Board and reference implementation. Device builders and camera vendors can minimize their design risks while reaping the benefits of Sony’s latest high-speed interface.

Accelerating Time to Market with Universal SLVS-EC RX IP Core

The FRAMOS SLVS-EC RX IP Core supports the complete SLVS-EC 2.0 standard with all its features, making it unique to the market. This IP Core enables easy integration of SLVS-EC sensors while minimizing the efforts and risks for customers implementing the interface from scratch, accelerating time to market and enhancing plannability. The IP Core itself is versatile, operates independently of the applied sensor, and supports the full range of pixel formats from 8 to 16 bit which can be dynamically changed at runtime. The automatic error detection and correction (ECC) feature, that is part of the IP core configuration, can be optionally activated when integrators need additional data transmission robustness. Furthermore, the IP Core features flexible lane support as well as support for overlapping ROIs, in line with the 2.0 standard.

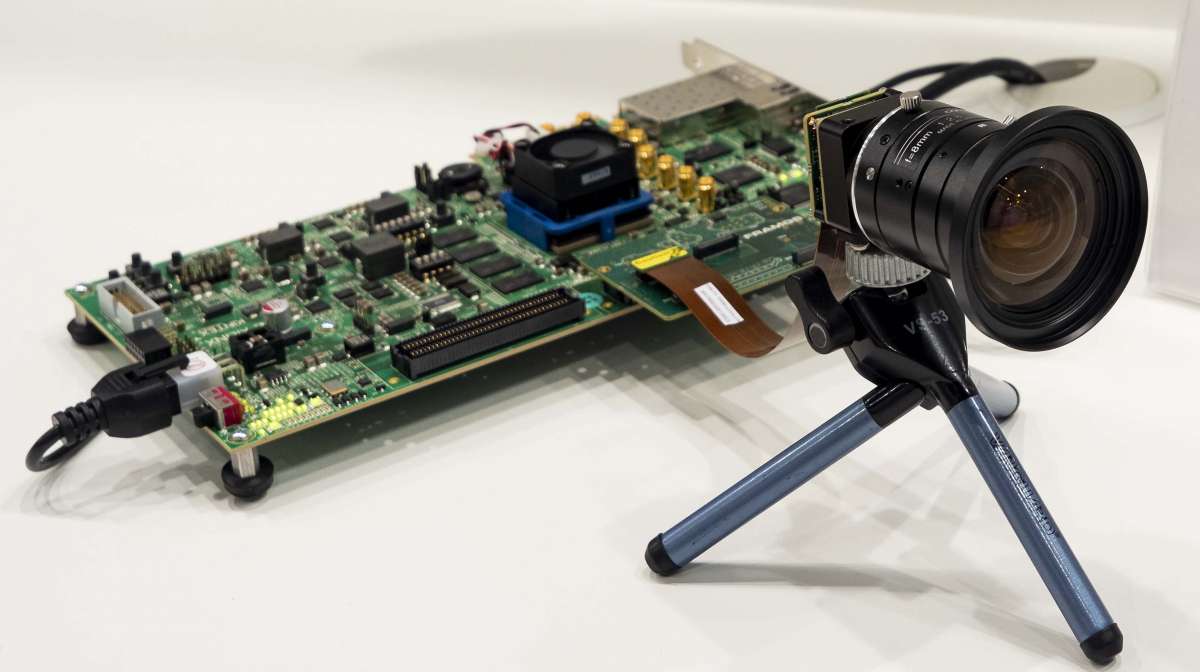

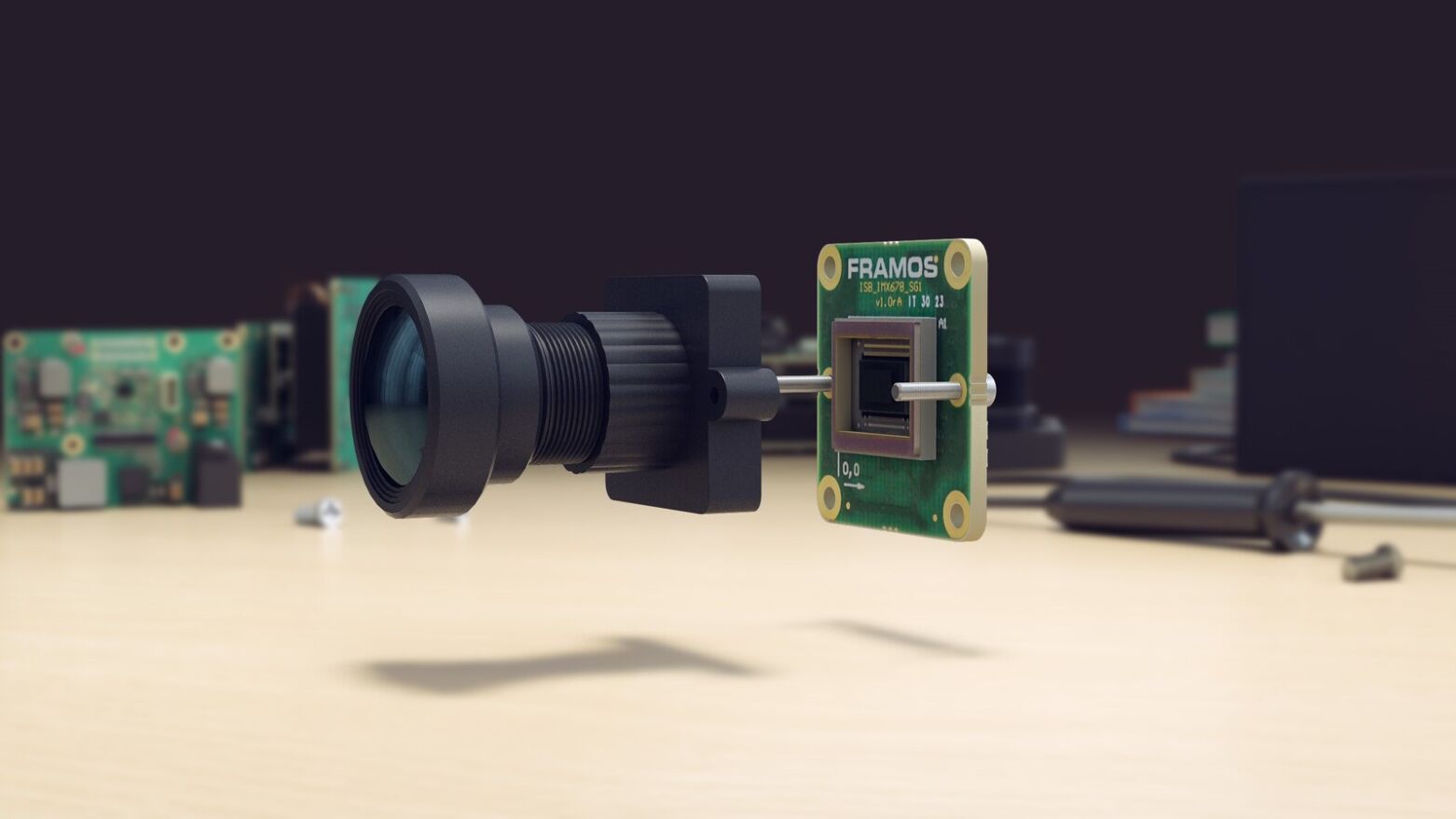

Comprehensive FRAMOS IP Core Development Kit

This Core Development Kit provides customers with a ready-to-use hardware environment which fully integrates into the FRAMOS Sensor Module Ecosystem. A fully documented basic image pipeline is provided with this kit that allows for evaluation, extension and integration of this IP core into typical camera designs. The package comes with the FRAMOS Sensor Module (FSM), the Framos Sensor Adapter (FSA) and the Framos Processor Adapter (FPA). Also included in the kit are a flex cable, tripod adapter and a software bundle containing the evaluation version of the SLVS-EC RX IP Core and a reference design example. This kit provides a complete evaluation platform to evaluate not only the IP core but the sensor performance as well, considerably reducing time to market.

Chris Baldwin, FPGA IP Expert and Technical Service Manager at FRAMOS, says: “The new version SLVS-EC 2.0 offers many advantages for customers. It supports faster sensors, slimmer designs, longer cable lengths, and is characterized by increased robustness with error detection and correction.”

Unlock SLVS-EC 2.0 Advantages

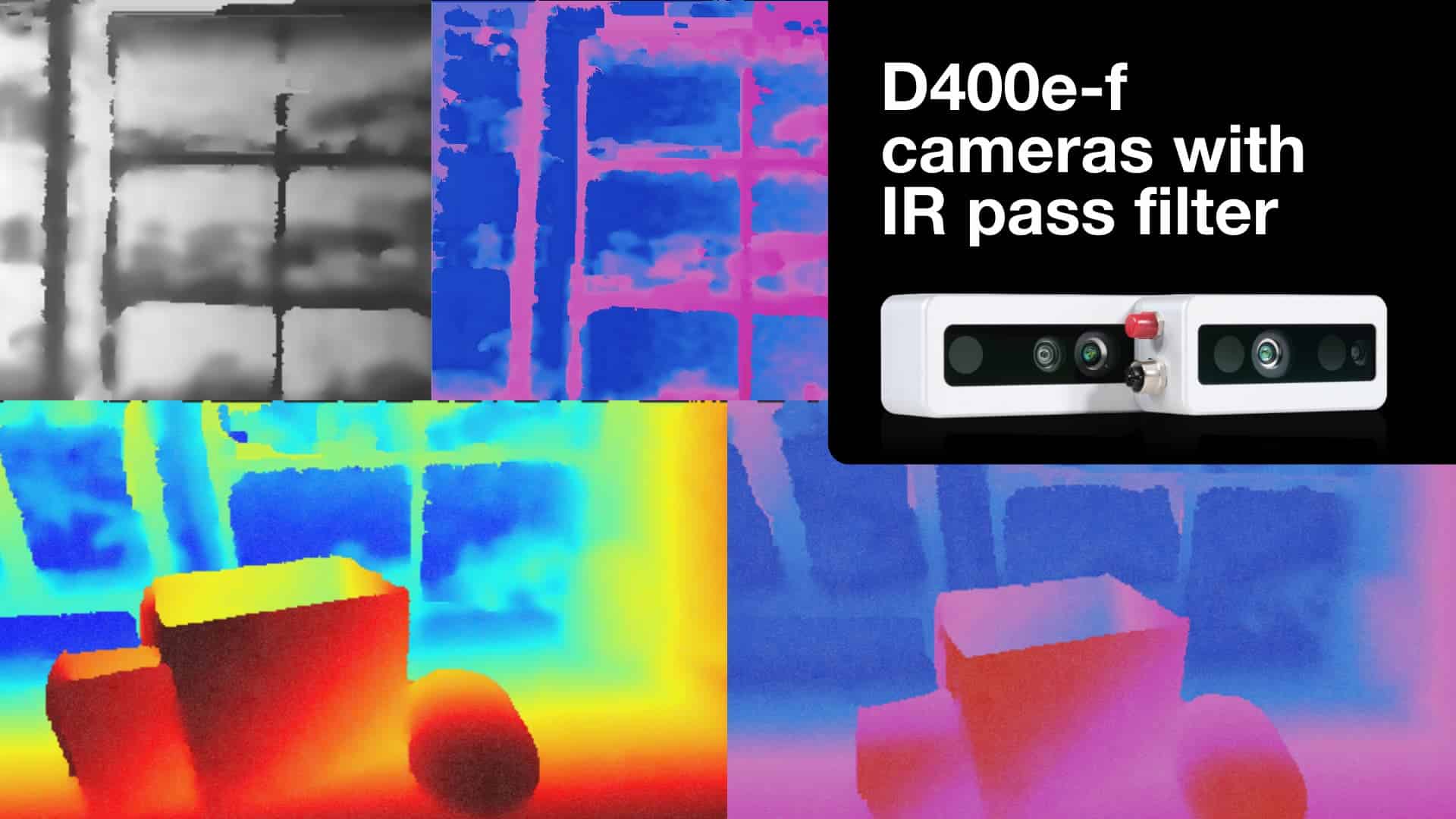

SLVS-EC 2.0 fully exploits the performance of the latest premium sensor technology, such as Sony’s Pregius S (Gen. 4) series, as well as upcoming CMOS sensors. Even for lower bandwidth systems, SLVS-EC allows greater design freedom, easier PCB designs and more robust signal paths, with its fewer pins and tracks needed for implementation. Some of the more common issues that a camera designer faces, such as the introduction of noise from having many complex components on a PCB, are minimized with implementing SLVS-EC. In addition, longer signal paths can be implemented that have higher tolerances and provide greater flexibility with interconnects and cabling, when compared to similar interfaces like SLVS, Sub-LVDS, MIPI CSI-2 implementations. Together, with its embedded clock, and error detection and correction capabilities, SLVS-EC 2.0 meets the requirements for state-of-the-art embedded vision systems.

Various Application in Diverse Markets

“With the introduction of SLVS-EC 2.0, we see the increased need for more bandwidth using a predefined standard protocol with feature rich interfaces that can simplify integrations, at the sensor level. We see many applications benefiting from fast design cycles and new generation of sensors because of this technology”, says Andre Brela, Embedded Vision Product Manager at FRAMOS. “This latest premium sensor features reduce design efforts for industrial high-speed and batch scanning systems, while transferring high data volumes over dozens of LVDS data lanes. Specialized imaging projects that require robust data transfer over cabling, such as satellite imagery, area mapping, digital high-resolution capturing, document scanning, or microscopy, will leverage this technology to its full extent.”

Further information

- IP Core: Encrypted RTL (VHDL), Source VHDL available, Simulation Environment (ModelSim)

- Documentation: User Manual, Reference Design Example for EK-U1-KCU105-G

- Verified Xilinx Devices: Artix-7, Kintex-7, Zynq-7000, Kintex US, Kintex US+, Zynq US+

- Reference implementation: Xilinx KCU105-G development kit

- Software availability from end of November 2020