# **Datasheet**

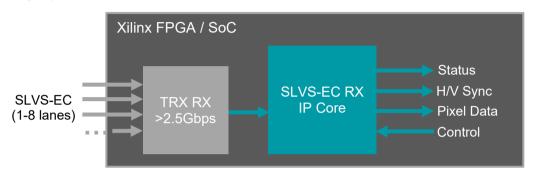

## SLVS-EC v2.0 RX IP Core for Xilinx FPGAs & SoCs

The SLVS-EC interface standard has emerged as the high-speed interface for image sensors from Sony. It increases throughput to up to 5 Gbit/s per lane at great signal integrity. Engineers developing solutions using Xilinx FPGAs and SoCs can take advantage of FRAMOS's SLVS-EC RX IP Core, Development Kit, and tested source code examples. Device builders and camera vendors can mitigate design risk while leveraging the benefits of Sony's latest high-speed interface.

## **Key Benefits & Features:**

- Byte-to-pixel conversion for SLVS-EC v1.2 / v2.0

- De-risk integration, reduce time to market

- Reference implementation for evaluation and guidance

- Flexible Lane Support in one IP Core

- Support for all supported RAW bit-depths

- Error correction and ROI overlap support

- AXI4 communication and control

## **Package**

#### IP Core

- **Encrypted RTL**

- Source Code Option (VHDL or Verilog)

- Simulation Environment (ModelSim)

#### **Documentation**

- **User Manual**

- Reference Design Example for EK-U1-KCU105-G

## **Verified Xilinx Devices (IP Core)**

- Artix-7 (xc7a200tfbg676-2)

- Kintex-7 (xc7k325tffg900-2)

- Zynq-7000 (xc7z045ffg900-2)

- Kintex US (xcku040-ffva1156-2-e)

- Kintex US+ (xcku5p-ffvb676-2-e)

- Zynq US+ (xczu9eg-ffvb1156-2-i-es2)

- Kria™ K26 (xck26)

| <b>Product Specification</b>                                       |                                                                                                                                                                       |  |  |  |  |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Name                                                               | SLVS-EC RX IP Core for Xilinx                                                                                                                                         |  |  |  |  |  |

| Туре                                                               | Receiver (RX)                                                                                                                                                         |  |  |  |  |  |

| Input Interface                                                    | SLVS-EC V1.2 and V2.0                                                                                                                                                 |  |  |  |  |  |

| Output Interface                                                   | Pixel Bus                                                                                                                                                             |  |  |  |  |  |

| Control Interface                                                  | AXI4-Lite                                                                                                                                                             |  |  |  |  |  |

| <b>Dynamic Mode Change</b>                                         | Yes (Pixel Format)                                                                                                                                                    |  |  |  |  |  |

| <b>Design Environment</b>                                          | Vivado Design Suite 2016.4 and later                                                                                                                                  |  |  |  |  |  |

| Supported Standard and Features                                    |                                                                                                                                                                       |  |  |  |  |  |

| Supported Standard and                                             | d Features                                                                                                                                                            |  |  |  |  |  |

| Supported Standard and Compatible Standards                        | SLVS-EC v1.2, v2.0                                                                                                                                                    |  |  |  |  |  |

|                                                                    |                                                                                                                                                                       |  |  |  |  |  |

| Compatible Standards                                               | SLVS-EC v1.2, v2.0                                                                                                                                                    |  |  |  |  |  |

| Compatible Standards Lanes Supported                               | SLVS-EC v1.2, v2.0<br>1, 2, 4, 8 (configurable by user)                                                                                                               |  |  |  |  |  |

| Compatible Standards Lanes Supported Baud Grade(s)                 | SLVS-EC v1.2, v2.0<br>1, 2, 4, 8 (configurable by user)<br>[1]: <b>1.2 Gbps</b> , [2]: <b>2.5 Gbps</b> , [3]: <b>5 Gbps</b><br>8, 10, 12, 14, 16 bits per pixel (RAW) |  |  |  |  |  |

| Compatible Standards Lanes Supported Baud Grade(s) Pixel Format(s) | SLVS-EC v1.2, v2.0  1, 2, 4, 8 (configurable by user)  [1]: 1.2 Gbps, [2]: 2.5 Gbps, [3]: 5 Gbps  8, 10, 12, 14, 16 bits per pixel (RAW)  (Dynamic Mode Change)       |  |  |  |  |  |

## **Resource Utilization**

The resource utilizations for the various configurations of the IP Core is shown below<sup>1</sup>:

| Configuration  | 1-lane |      | 2-lanes |      | 4-lanes |      | 8-lanes |       |

|----------------|--------|------|---------|------|---------|------|---------|-------|

| Error Handling | CRC    | ECC  | CRC     | ECC  | CRC     | ECC  | CRC     | ECC   |

| Look-up Tables | 643    | 2732 | 984     | 3725 | 1561    | 6100 | 3122    | 10520 |

| Flip-Flops     | 1181   | 2467 | 1538    | 3059 | 2279    | 4174 | 4045    | 6575  |

| 18k BRAMs      | 0      | 0    | 0       | 0    | 0       | 1    | 0       | 2     |

| 36k BRAMs      | 0      | 5    | 0       | 5    | 0       | 4    | 0       | 5     |

| DSPs           | 0      | 3    | 0       | 3    | 0       | 3    | 0       | 3     |

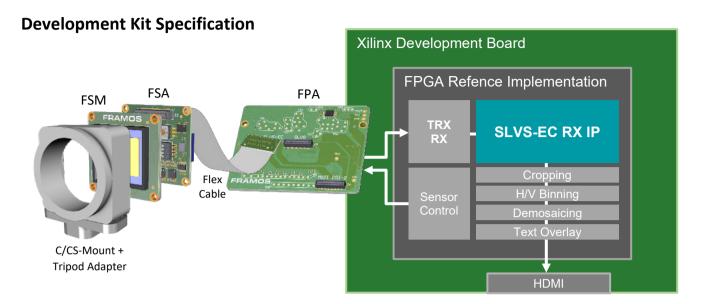

## **Development Kit**

The SLVS-EC RX IP Core Development Kit from FRAMOS provides you with a ready-to-use hardware environment. It supports your evaluation and demonstrates based on an exemplary and fully documented image pipeline, the integration of the IP Core into a typical camera design.

#### **Order Codes**<sup>2</sup>:

- FSM-IMX421C/XX1\_Devkit-SLVS+EC Sony IMX421LQJ, 2.8MP Pregius (Gen 3)

- FSM-IMX530C/XX1\_Devkit-SLVS+EC Sony IMX530-AAQJ, 24MP Pregius S (Gen 4)

Version 1.0d from 2023-04-13

<sup>&</sup>lt;sup>1</sup> Numbers are rounded maximum values and apply to all verified devices. Source: Utilization reports of Vivado Design Suite 2017.4.

<sup>&</sup>lt;sup>2</sup> Xilinx Development Board is not included and available from your local Xilinx partner.

## **Hardware Specification**

## **Package**

- FRAMOS Sensor Module (FSM) with C/CS-Mount

- FRAMOS Sensor Adapter (FSA)

- Framos Processor Adapter (FPA)

- Flex Cable 150 mm

- ¼" Tripod Adapter

- Software Download

The Development Kit is a component of the *FRAMOS Sensor Module Ecosystem* and the hardware compatibility exceeds the scope of the IP Core offering. For further information, refer to the appropriate FSM Datasheet.

### Hardware Compatibility<sup>3</sup>:

- Artix-7<sup>™</sup> (EK-A7-AC701-G)

- Kintex-7<sup>™</sup> (EK-K7-KC705-G)

- Zynq-7000™ (EK-Z7-ZC706-G)

- Kintex UltraScale™ (EK-U1-KCU105-G)

- Kintex UltraScale+™ (EK-U1-KCU116-G)

- Zynq UltraScale+™ (EK-U1-ZCU102-G)

## **Software Specification**

#### **Package**

- Reference Design Example for EK-U1-KCU105-G<sup>4</sup>

- SLVS-EC RX IP Core for Evaluation (Time Bombed)

- Documentation

- Reference Design Example description

- IP Core User Manual

#### Reference Design Example for Xilinx KCU105-G:

- Supported imagers: FSM-IMX421, FSM-IMX530<sup>4</sup>

- Instantiation SLVS-EC RX IP Core

- Image sensor configuration (Binary)

- Master mode (free run)

- 8-Lane SLVS-EC streaming

- 10 / 12 bit pixel data

- Full resolution

- Xilinx Transceiver configuration

- Cropping and binning of RAW image stream

- Demosaicing (Bayer to RGB conversion)<sup>5</sup>

- Text overlay (adding statistics)<sup>5</sup>

- 1080p60 output via HDMI (Xilinx Dev. Kit)

## **Software Compatibility**

Requires Vivado Design Suite 2020.2.

If you have additional questions about this technology, how it would benefit you or want to request project specific image sensor integration support, please direct your request to our FRAMOS imaging experts. We can be reached at: info@framos.com

<sup>&</sup>lt;sup>3</sup> Supported only in hardware, greyed kits require customers to modify the Vivado Reference Design.

<sup>&</sup>lt;sup>4</sup> Adjustments to reference design as well as sensor integration and configuration are not part of the IP Core offering.

<sup>&</sup>lt;sup>5</sup> Using standard Xilinx LogiCOREs