FRAMOS SLVS-EC RX IP CORE

Why a SLVS-EC IP COre

SLVS-EC

Scalable Low Voltage Signaling with Embedded Clock)

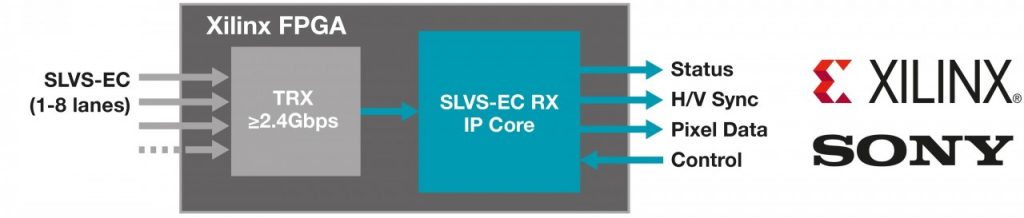

Sony’s SLVS-EC interface standard has emerged as the best high speed interface to Sony’s best image sensors, enabling higher throughput, greater signal integrity, and simpler designs. Engineers developing solutions using Xilinx FPGAs and SoCs can take advantage of FRAMOS’s SLVS-EC RX IP Core, Evaluation Board and tested source code examples. Device builders and camera vendors can de-risk the design while reaping the benefits of Sony’s latest high-speed interface.

7 Key Benefits of our IP Core

![]()

Byte-to-pixel conversion for SLVS-EC v1.2 / v2.0

![]()

De-risk integration, reduce time to market

![]()

Reference implementation for evaluation and guidance

![]()

Flexible Lane Support in one IP Core

![]()

Support for all common RAW bit-depths

![]()

Error correction and ROI overlap support

![]()

AXI4-Lite communication and control

While benefitting from the outstanding sensor performance, SLVS-EC’s technological advantages allow significantly simplified designs while extending cable lengths and maintaining signal integrity at high data rates. The SLVS-EC RX IP Core for Xilinx FPGAs and SoCs provides a trusted, known-good implementation of Sony’s preferred interface to advanced image sensors. FRAMOS offers help with the SLVS-EC to keep internal development teams focused on their core competencies.

SLVS-EC RX IP Core for Xilinx FPGAs

The FRAMOS SLVS-EC RX IP Core is a receiver that handles the byte-to-pixel conversion of the incoming image data stream. The IP Core provides the customer‘s FPGA code with a Parallel Pixel Interface (PPI) from the transceivers of the Xilinx FPGA or SoC. Expect versatile support for all SONY sensors that support SLVS-EC version 1.2 and 2.0, at the maximum bit rate, regardless of the number of lanes or bit depth that are required.

IP Core

Encrypted RTL

Source Code Option (VHDL or Verilog)

Simulation Environment (ModelSim)

Documentation

User Manual

Reference Design Example

Supported Device Architectures

Xilinx 7 Series, UltraScale, UltraScale+ and Kria™ Families.

Supported devices are available on request.

PARAMETER | VALUE |

|---|---|

Product Name | SLVS-EC RX IP Core for Xilinx

|

Standard Version | SLVS-EC v1.2, v2.0

|

Type | Receiver (RX)

|

Control Interface | AXI4-Lite |

Input Interface | SLVS-EC V1.2 and V2.0 |

Lanes Supported | 1, 2, 4, 8 (configurable by user) |

Baud Grade(s) | [1]: 1.2 Gbps, [2]: 2.5 Gbps, [3]: 5 Gbps |

Pixel Format(s) | 8,10,12,14,16 bits per pixel (RAW) (Dynamic Mode Change) |

Dynamic Mode Change | Yes (Pixel Format) |

CRC / ECC | Supported (Configurable) |

Embedded Data | Supported |

ROI Overlapping | Supported |

| Name | Manufacturer | Product Type | Specification | Target Device Type | Supported Devices |

|---|---|---|---|---|---|

| SLVS-EC v2.0 RX IP Core Xilinx Source | FRAMOS GmbH | IP Core, Source Code (VHDL, Verilog) | Support Sony SLVS-EC v1.2 and v2.0 | FPGA, SoC | Xilinx Artix-7™, Kintex-7™, Zynq-7000™ SoC, Kintex UltraScale™, Kintex UltraScale+™, Zynq UltraScale+™ MPSoC, Kria™ K26 |

| SLVS-EC v2.0 RX IP Core Xilinx Encrypted | FRAMOS GmbH | IP Core, Encrypted RTL | Support Sony SLVS-EC v1.2 and v2.0 | FPGA, SoC | Xilinx Artix-7™, Kintex-7™, Zynq-7000™ SoC, Kintex UltraScale™, Kintex UltraScale+™, Zynq UltraScale+™ MPSoC, Kria™ K26 |

Articles & Downloads

Article “Shorten the Time-to-Market“

Flyer “FRAMOS SLVS-EC RX IP Core“